2023年4月4日上午10点,微纳电子学系校企共建研究生课程“集成电路设计前沿技术”第二讲在中院413教室顺利展开,由孙亚男老师和杨志老师共同主持。

课程有幸邀请到华为海思半导体有限公司的技术专家李益航作主讲人,为同学们带来有关ASIC后端物理设计知识的讲解。

课程开始,李益航回顾了硅谷的发展历史,概述了芯片设计的发展历史和摩尔定律。之后,专家以工艺的演进对芯片设计的影响作为切入点,引出本次讲座的主题——芯片物理设计技术。

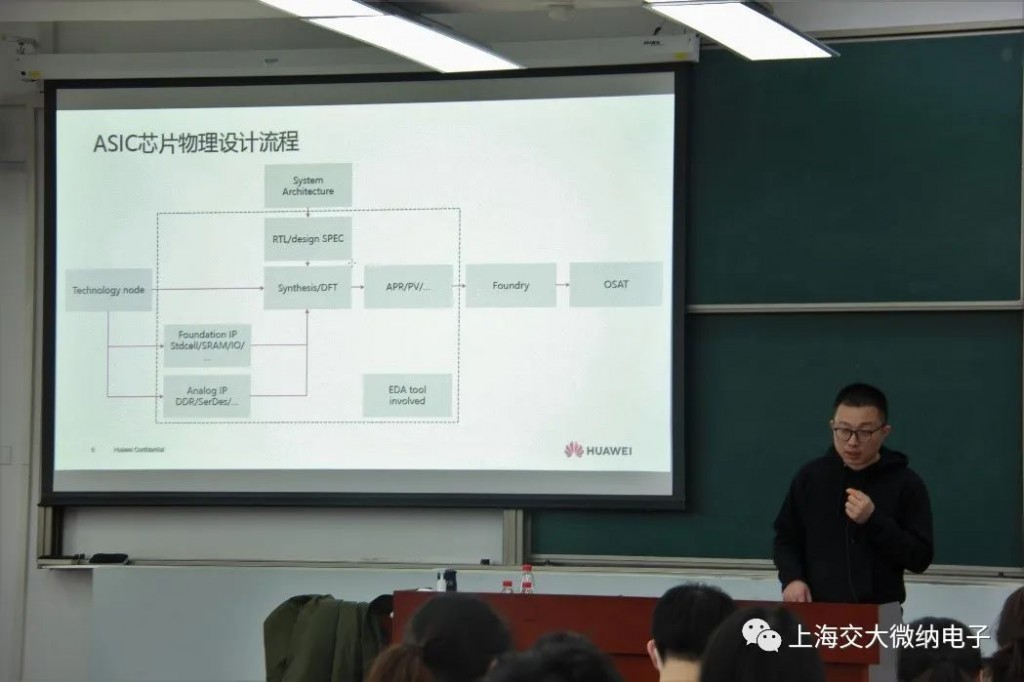

图一 专家介绍ASIC芯片设计整体流程

李益航为同学们介绍了ASIC芯片物理设计的基本流程。芯片的物理设计流程涵盖了从RTL代码到最终输出GDS文件的全部流程,是对多个电路的多个不同指标,如电路面积,走线长度和功耗等,进行优化的过程。同时,专家也向同学们介绍了芯片物理设计中的一些常见技术,如DVFS、AVS等。

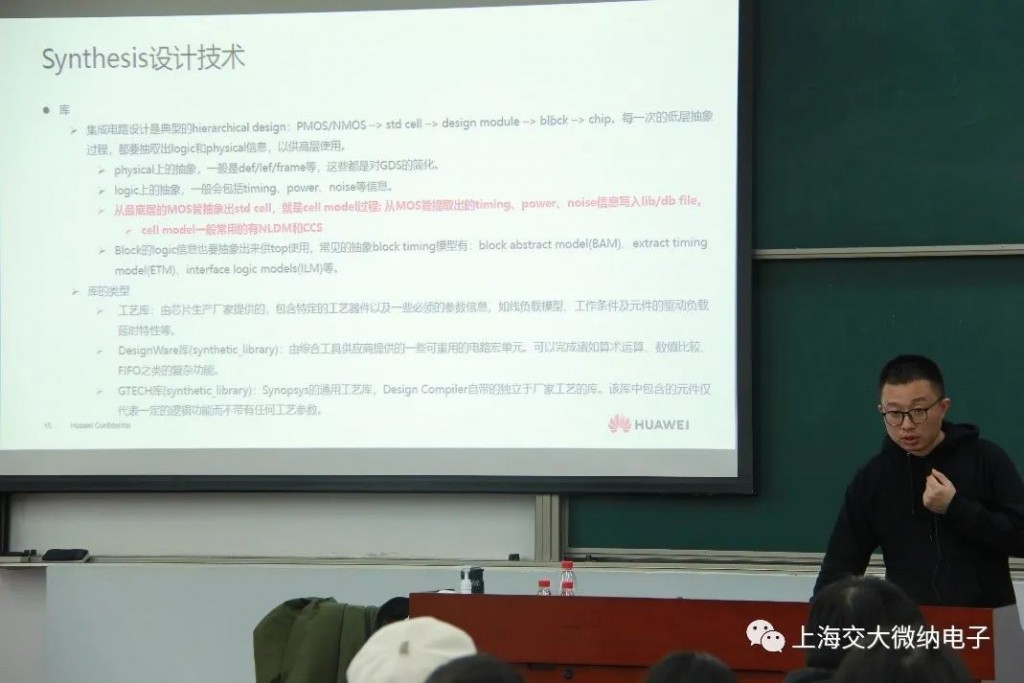

图二 专家介绍STA静态时序分析技术

之后,李益航重点向大家介绍了芯片物理设计流程中的synthesis综合设计技术。综合设计技术将RTL代码转换成电路门级网表,其中包括综合环境设置、单元库链接、设计载入等多个步骤。综合设计的对象包括单元、网络、时钟等多个层级。

图三 专家介绍STA静态时序分析技术

下半场讲座,李益航继续为介绍synthesis综合设计技术,包括STA静态时序分析技术、CRPR路径移除技术等。同时,专家也为同学们介绍多种非理想因素,如信号间的串扰、电路工艺扰动等,对电路设计的影响。专家以多个案例,帮助大家更好地理解综合时序优化技术。

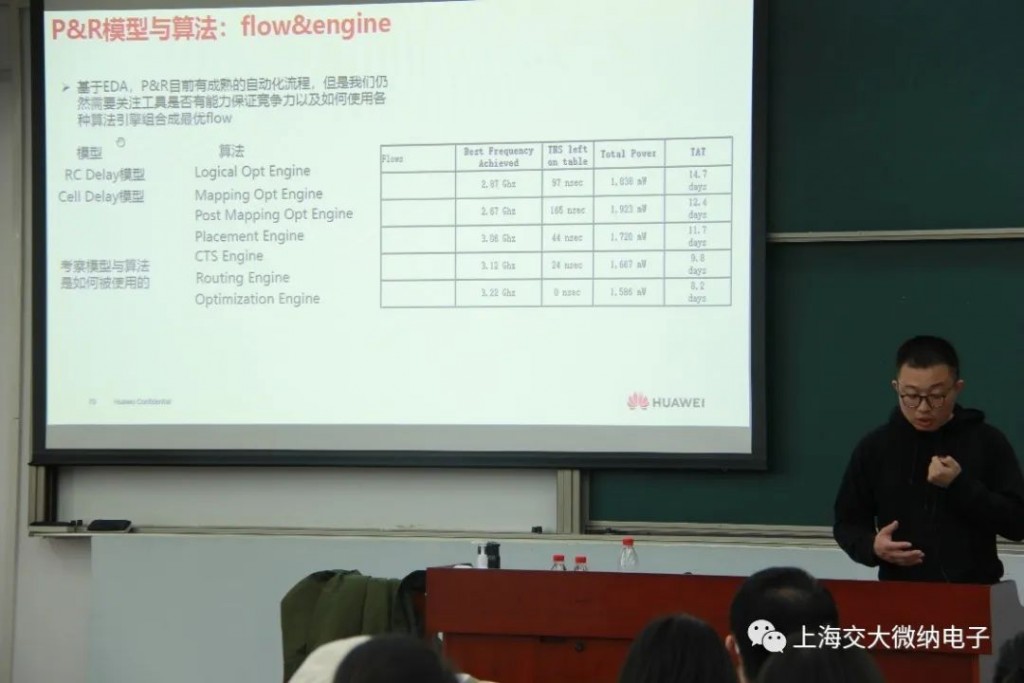

图四 专家讲解芯片设计的布局布线技术

最后,李益航还与同学们分享了芯片设计中的布局布线技术,通过优化线长的方式来简化布局布线问题。同时,专家还分享了多种线长近似模型和布局布线算法。目前,基于EDA工具,布局布线已有成熟的自动化流程,但我们仍然需要关注算法的竞争力。

图五 孙亚男老师和杨志老师为专家颁发授课证书

本次讲座进入尾声,同学们为专家献上了热烈的掌声,相信同学们在这次讲座后对芯片后端物理设计流程有了更加深入的了解。课间,孙亚男老师和杨志老师也为李益航专家颁发了授课证书。

撰稿人:徐浏凯

责任编辑:张媛